iMedPub Journals www.imedpub.com **2019** Vol.3 No.1:1

# Insights of Trap Level Effect on the Performance of InAIN/GaN High Electron Mobility Transistor (HEMT)

# Abstract

InAlN/GaN high electron mobility transistor (HEMT) structures with appropriate barrier thickness are designed to investigate the effects of trap level on the device's performance. Based on the two-dimensional drift-diffusion simulation, the influence of five trap levels of 0.3, 0.36, 0.42, 0.6 and 0.95 eV below the conduction band minimum on the DC characteristics of InAlN/GaN HEMTs are described. The results indicate that the depth of trap level obviously affects the drain current and threshold voltage of the devices, which is mainly attributed to the varied trapping rate for electrons at different trap levels according to the Shockley-Read-Hall (SRH) recombination process.

Keywords: InAIN/GaN HEMT; Barrier layer thickness; Trap level; DC characteristics

Received: January 30, 2019; Accepted: February 11, 2019; Published: February 14, 2019

#### Zhenzhong Yu\*, Huiwu Hong, Qigao Fan and Yixin Zhu

Department of Internet of Things Engineering, Jiangnan University, Wuxi 214122, China

#### \*Corresponding author: Zhenzhong Yu

yzzhong2018@163.com

Zhenzhong Yu, Department of Internet of Things Engineering, Jiangnan University, Wuxi 214122, China

Tel: +051085913623

**Citation:** Yu Z, Hong H, Fan Q, Zhu Y (2019) Insights of Trap Level Effect on the Performance of InAIN/GaN High Electron Mobility Transistor (HEMT). J Nanosci Nanotechnol Res Vol.3 No.1:1

# Introduction

Over the years, as a typical representative of the third-generation wide bandgap semiconductor materials, gallium nitride (GaN) has attracted enormous attention due to its high critical electric field, polarization induced a large amount of electron gas, higher electron mobility and high saturation velocity [1,2] and the growth of AlGaN/GaN heterostructure allows to achieve high electron mobility transistors (HEMTs) with higher breakdown voltage, lower on-resistance and high operation switching frequency [3,4]. However, the AlGaN/GaN heterojunction structure suffers lattice defects due to lattice mismatch and piezoelectric effect, leading to reliability problems that have restricted the development of AlGaN/GaN heterojunction devices [5-8]. Recently, InAIN/GaN appears as a new type III-nitride heterojunction structure [9,10]. The In Al, N can be made lattice matched to GaN epilayer when the In composition of In Al, N is 0.17 [11]. The heterojunction conduction band is more discontinuous than that of AIGaN/ GaN, exceeding 1 eV [11], and In Al, N-based HEMTs exhibit higher 2DEG density thereby enabling higher drain current [12]. Moreover, In<sub>0.17</sub>Al<sub>0.83</sub>N/GaN heterostructure only produce spontaneous polarization which improves the reliability of the devices [10-13].

On the other hand, the presence of surface, bulk, or interface trap states can affect the performance of GaN-based HEMTs significantly [14]. Usually, the surface traps are considered to be

factors of drain lag [15,16]. Therefore, a large amount of attention has been focused on the effects of taps on the performance of GaNbased HEMTs. Various experimental methods were employed to determine the location of traps in HEMTs, and investigated the trap-related device characteristics [17-20]. Iron-doping induced surface trap states or barrier layer trap states were explored to improve the performance of GaN-based HEMTs [21-23]. However, most of these analysis only focused on the traps on the surface or in the AlGaN barrier layer, little attention has been performed on the trapping effect in the unintentionally doped (UID) GaN buffer layers for GaN-based HEMTs. As GaN contains a high density of dislocation and various undesired complexes, impurities, and point defects, there are intrinsic trap levels in the UID GaN buffer layers. Thus, it is essential to investigate the effects of trap level in UID GaN on the performance of GaN-based HEMTs.

In this work, we firstly propose an  $In_{0.17}AI_{0.83}N/GaN$  HEMT structure with optimized  $In_{0.17}AI_{0.83}N$  barrier thickness in terms of the threshold voltage and saturation drain current ( $I_{D,max}$ ) based on the Silvaco TCAD simulation, and then theoretically explore the effects of different trap levels in the UID GaN buffer layer on devices' performance. As it is unclear of the exact trap level in the UID GaN buffer layer, we reasonably consider five accepter-like traps in the GaN buffer according to some experimental

studies on the location of traps in GaN [24-26], with the energy levels of 0.3, 0.36, 0.42, 0.6 and 0.95 eV, respectively, below the conduction band minimum [27,28]. The results indicate that different trap levels result in specific  $I_{D,max}$  and off-state leakage current values, which is crucial for the DC characteristics of GaN-based HEMT. Furthermore, the underlying physical mechanisms of the trap level effect on the performance of  $In_{0.17}AI_{0.83}N/GaN$  HEMT have been explored by the recombination model and energy band analysis.

#### **Device Description and Physical Models**

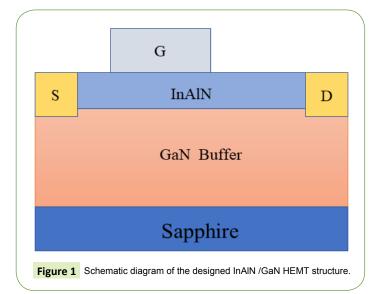

**Figure 1** shows the schematic diagram of the designed latticematched  $In_{0.17}AI_{0.83}N/GaN$  HEMT with asymmetric gate position. The epitaxial structure was composed of a 1 µm unintentionally dopped GaN buffer layer, with a background carrier concentration of  $1 \times 10^{16}$  cm<sup>-3</sup> [29], and a thin layer of InAIN barrier. Ohmic contacts were formed in the source and drain terminals. The distance of gate-source, gate-drain, and length of gate were 0.5 µm, 10 µm, and 2 µm, respectively. The device surface was passivated by using Si<sub>3</sub>N<sub>4</sub> thin film to reduce the current collapse effect in the HEMT [30]. It was demonstrated that the thickness of AlINN barrier layer could strongly affect the 2DEG density in the InAIN/GaN interface. Therefore, reasonable barrier thickness of 15, 20 and 25 nm were selected to optimize the HMET device structure according to experimental results [31,32], while a trap density of  $5 \times 10^{16}$  cm<sup>-3</sup> was set in the UID GaN buffer layer.

In the calculation process, the drift-diffusion transport model was used to simulate the device response, with several important physical models of polarizations, Shockley-Read-Hall (SRH), the low field electron mobility, and high field mobility included in simulations.

Polarization modeling is critical for GaN based devices. Here,  $P_{PE}$  and  $P_{SP}$  represent the piezoelectric polarization and spontaneous polarization. The total polarization-induced polarization charge density can be expressed [33-35] as:

$$P_{total} = [P_{PE}(bottom) + P_{SP}(bottom)] - [P_{PE}(top) + P_{SP}(top)]$$

(1)

With

$P_{SP}$  ( $In_x AL_{1-x}N$ )=-0.081+0.049x C/m<sup>2</sup>

$$P_{_{PE}}(In_x AL_{_{1-x}}N)=(-0.132+0.744x+0.035x^2)/(3.122+0.436x) C/m^2$$

$P_{_{SP}}$  (GaN)=-0.029 C/m<sup>2</sup>

The low field mobility model and high field mobility model have been used to consider various types of scattering mechanisms [32]. The low field mobility model is specified as below [34]:

$$\frac{1}{u(N,T)} = a(\frac{N}{1 \times 10^{17}})(\frac{T}{300})^{\frac{-3}{2}} \times ln[1 + 3(\frac{T}{300})^2(\frac{N}{1 \times 10^{17}})^{\frac{-2}{3}}] + b(\frac{T}{300})^{\frac{3}{2}} + \frac{c}{\exp\left(\frac{1065}{T}\right) - 1}$$

(2)

with  $a=2.61 \times 10^4/V.s.cm^{-2}$ ;  $b=9.8 \times 10^{-4}/V.cm^{-2}$  and  $c=1.7 \times 10^{-2}/s.m^{-2}$ .

Here, u(N,T) is the mobility as a function of doping and ambient

temperature, N is the total doping concentration and T is the ambient temperature. The high field mobility model is described as follows [36]:

$$u(E) = \frac{u(N,T) + v_{sat} \frac{E^{(N_1-1)}}{E_c^{N_1}}}{1 + a_n (\frac{E}{E_c})^{N_2} + (\frac{E}{E_c})^{N_1}}$$

(3)

where  $v_{sat}$  is saturation velocities, u(N,T) is the low field mobility and E is the electric field. The values of  $E_{c}$ ,  $a_n$ ,  $N_1$  and  $N_2$  can be referred [36]. A trap energy level within the bandgap is caused by a structural defect in GaN. SRH recombination occurs when an electron gets trapped, referring to a trap-assisted recombination process. In order to investigate the specific physical mechanism of electron trapping, the SRH recombination model for each single trap level is required to calculate the electron trapping process. The trapping rate [36-38] is given by:

$$R_{net}^{SRH} = \frac{pn - n_{ie}^{2}}{\tau_{p}[n + n_{ie}exp(\frac{E_{irap}}{kT})] + \tau_{n}[p + n_{ie}exp(\frac{-E_{irap}}{kT})]}$$

(4)

where  $E_{trap}$  is the difference between the trap energy level and the intrinsic Fermi level, *T* is the lattice temperature,  $n_{ie}$  is intrinsic carrier concentration.  $\tau_n$  and  $\tau_p$  are the lifetimes of electrons and holes, respectively, both of which are assumed to be 10<sup>-9</sup> *S*. In the formula, the electron density can be expressed as  $n = N_c \exp(\frac{E_{F_n} - E_c}{kT})$  according to Fermi statistics. When only the electron trapping effect is considered, the formula can be simplified to:

$$R_{net}^{SRH} = \frac{p}{\tau_p \left[1 + \frac{n_{ie}}{N_c \exp\left(\frac{E_{F_n} - E_c}{kT}\right)} exp\left(\frac{E_{trap}}{kT}\right)\right]}$$

(5)

As for the material parameters, based on LDA-1/2 approach [39], the band gap of Al In, N material can be calculated by:

$$E_g^{Al_x In_{1-x}N} = xE(AlN) + (1-x)E(InN) - bx(1-x)$$

(6)

with

*E* (*ALN*)=6.06 eV, *E* (*InN*)=0.95 eV, and *b*=3.4x+1.2

The permittivity of the material can be calculated [35] by:

$$\mathcal{E}_{Al_x In_{1-x}N} = -4.3x + 14.61$$

(7)

$$\mathcal{E}_{Al_x Ga_{1-x}N} = 0.03 \text{x} + 10.28 \tag{8}$$

The relevant physical parameters of materials are listed in Table 1.

#### **Results and Discussion**

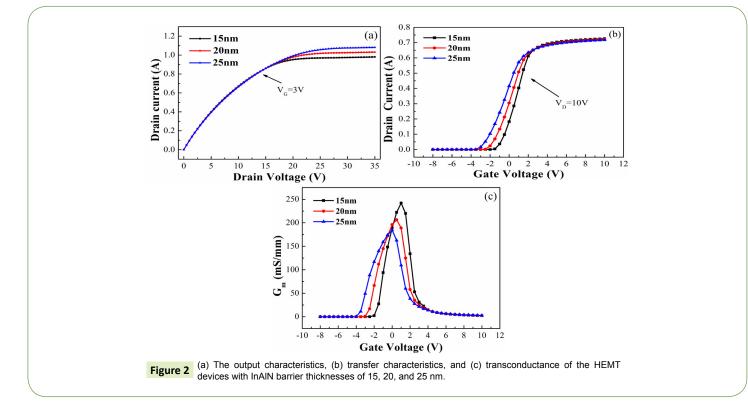

Figure 2 shows the direct-current (DC) characteristics of the

| Table 1 Parameters of Al <sub>0.83</sub> In <sub>0.17</sub> N | I and GaN sed in the simulation. |

|---------------------------------------------------------------|----------------------------------|

|---------------------------------------------------------------|----------------------------------|

| Parameter                                                                                  | GaN       | Al <sub>0.83</sub> In <sub>0.17</sub> N |

|--------------------------------------------------------------------------------------------|-----------|-----------------------------------------|

| Band gap [eV]                                                                              | 3.42      | 4.62                                    |

| Permittivity                                                                               | 10.28     | 11.04                                   |

| Hole mobility $[v^{-1}.s^{-1}.cm^2]$<br>$v_{sat}$ for electrons $[10^7 \text{ cm.s}^{-1}]$ | 22<br>2.0 | 82<br>1.1                               |

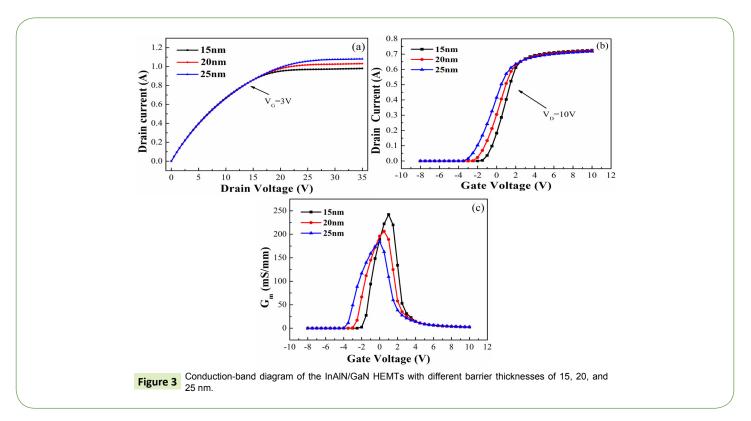

devices with three different InAIN barrier layer thicknesses of 15, 20, and 25 nm. **Figure 2a** depicts the output characteristics of the three devices with the gate voltage  $V_G$  set as 3 V, and the drain voltage  $V_D$  scanned from 0 to 35 V. It is observed that  $I_{D,max}$  of the HEMTs with 15, 20, and 25 nm InAIN barrier layer are about 0.98, 1.03, and 1.08 A, respectively, indicating that the saturated drain current increases as the increase of InAIN barrier layer thickness. **Figure 2b** shows the transfer characteristics of the three devices under  $V_D=10$  V. The threshold voltages are -1.25, -2.5, and -3.5 V for the devices with barrier thickness of 15, 20, and 25 nm, respectively, and present a negative shift as the barrier thickness increases. **Figure 2c** exhibits the effect of barrier thickness variation on the transconductance of the InAIN/GaN HEMTs. The obtained peak extrinsic transconductances are 242, 206 and 184

ms/mm at  $V_p$ =10 V for the three devices, respectively. In order to explore the dependence of the devices, DC characteristics on barrier thickness. **Figure 3** simulated the conduction band diagram of the three HEMTs at  $V_g$ =3 V. The results reveal that the depth of the electron potential well increases with the increase of barrier thickness at the InAIN/GaN interface. That would cause more electrons collection in the potential well with thicker InAIN layer, which results in the largest  $I_{D,max}$  and negative threshold voltages of the device with 25 nm barrier thickness.

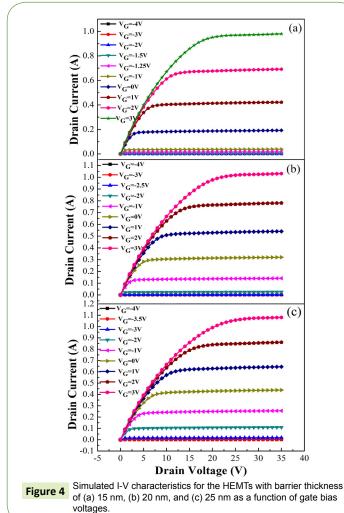

**Figure 4** shows I-V characteristics at different gate bias voltages for the InAIN/GaN HEMTs with three different barrier layer thicknesses. Can be seen that the pinch-off behavior is improved as the InAIN barrier layer thickness decreases. The cut-off phenomenon occurs at  $V_{g}$ =-1, -2 and -3 V for the devices with barrier thickness of 15, 20, and 25 nm, respectively, which is due to the fact that a smaller thickness of the barrier layer would cause low 2DEG density and negative threshold voltage [22], resulting in the improved pinched-off performance for HEMTs. Considering the effects of InAIN barrier thickness on both the DC and pinched-off characteristics, optimized structure of HEMT with 20 nm InAIN barrier thickness is chosen to investigate the influence of trap levels in UID GaN on the performance of InAIN/ GaN HEMTs.

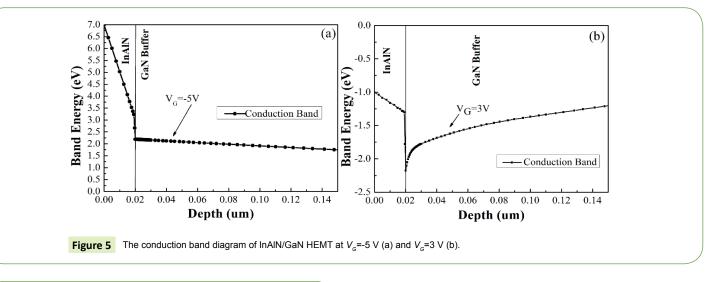

To explore the effects of different trap levels in the GaN buffer layer, five trap levels of 0.3, 0.36, 0.42, 0.6 and 0.95 eV below the conduction band minimum are chosen. These traps are assumed to be acceptor type traps which are unionized when  $V_G$  is below -1 V and will capture electrons when ionized. The conduction band diagrams of the HEMT structure in both the off- and onstate are simulated in **Figure 5** to investigate the distribution of carriers and further analyze the effects of different trap levels

2019

Vol.3 No.1:1

in UID GaN layer. The trap levels in the UID GaN cause changes in current that can be reflected by changes in the conduction band. As shown in **Figure 5a**, the HEMT under -5 V is pinched off, and few electrons exist at the InAIN/GaN interface. In **Figure 5b**, the HEMT under 3 V is pinched on, and the electrons would be confined in the potential well at the InAIN/GaN heterojunction interface. The depth of the electron potential well increases significantly when the device is under on-state, resulting in the variation of the  $I_{Drmax}$  values.

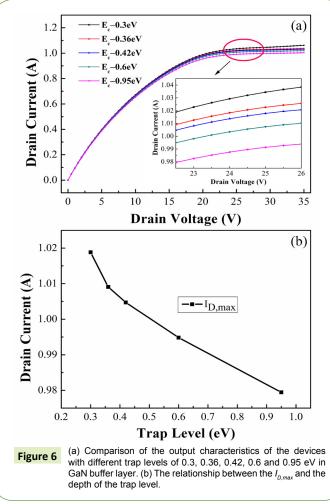

**Figure 6a** shows the I-V characteristics of the devices with different trap levels of 0.3, 0.36, 0.42, 0.6 and 0.95 eV in GaN buffer layer at  $V_c$ =3 V. As can be seen from the inset of **Figure 6a**, which is corresponding to the magnification of the circled area, it is evident that the five different trap levels cause different saturation currents. The  $I_{D,max}$  of the device with the trap level of 0.3 eV presents the largest value of 1.02 A, while that of the device with the trap level of 0.98 A. The saturation current as a function of the trap level is shown in **Figure 6b**, which indicates that the  $I_{D,max}$  decreases as the depth of the trap level increases.

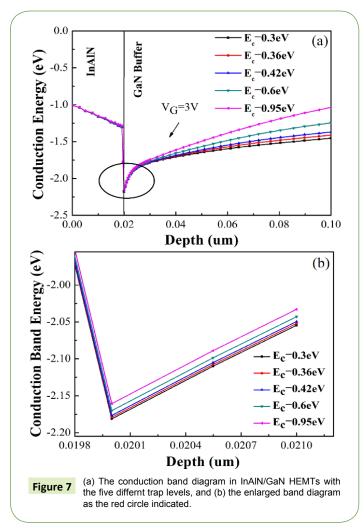

To further investigate the impacts of different trap levels in UID GaN buffer layer on  $I_{D,max}$  and the distribution of carriers, the conduction band diagrams of the devices with five trap levels of  $E_c$ -0.3 eV,  $E_c$ -0.36 eV,  $E_c$ -0.42 eV,  $E_c$ -0.6 eV and  $E_c$ -0.95 eV at  $V_G$ =3 V are shown in **Figure 7a.** The electrons would be confined in the potential well at the InAIN/GaN heterojunction interface, since the InAIN/GaN HEMT is normally-on. **Figure 7b** displays the magnification of the circled area in **Figure 7a**, it is obviously seen that the height of the potential well decreases as the depth of trap level increases, which is due to the different trapping rates caused by different trap levels. According to Eq. (5), the parameter

**2019** Vol.3 No.1:1

$R_{net}^{SRH}$  is effected by the value of  $E_{trap}$ , and the increase of  $E_{trap}$  can decrease the value of  $R_{net}^{SRH}$ . As  $E_{trap}$  is the difference between the trap energy level and the intrinsic Fermi level, the device with  $E_c$ -0.3 eV has the largest value of  $E_{trap'}$  while  $E_{trap}$  of the device with  $E_c$ -0.95 eV is the smallest. Therefore, the most electrons tend to be captured at the largest trap level of  $E_c$ -0.95 eV.

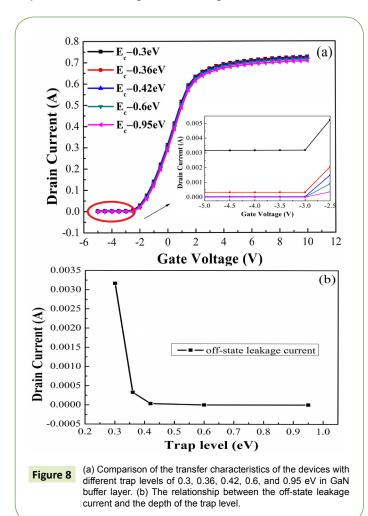

Figure 8a presents the transfer characteristics of the devices with different trap levels, and the enlarged region as the red circle

indicated is also presented, which reveals that the threshold voltages for the five structures are almost the same of about -V. However, the off-state leakage current shows obvious variations due to different trap levels. From the relationship between the off-state leakage current and the depth of the trap level shown in **Figure 8b**, it can be seen that the trap level with the smallest depth of  $E_c$ -0.3 eV exhibits the largest off-state leakage current of 3.3 mA.

**2019** Vol.3 No.1:1

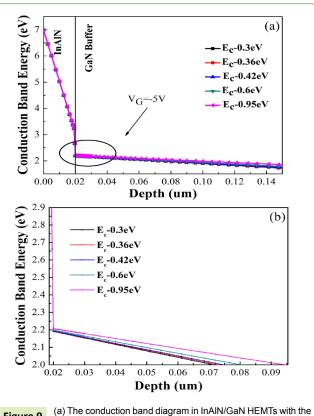

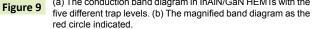

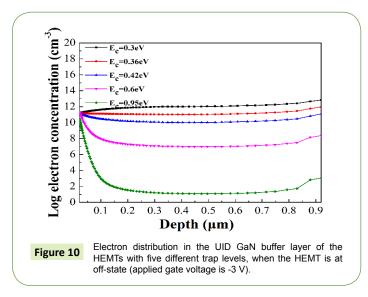

In order to explore the effects of different trap levels in the UID GaN buffer layer on the off-state leakage current, the conduction band diagram of the devices with five trap levels of  $E_c$ -0.3 eV,  $E_c$ -0.36 eV, E<sub>c</sub>-0.42 eV, E<sub>c</sub>-0.6 eV and E<sub>c</sub>-0.95 eV under pinch-off state are simulated in Figure 9a. It can be seen that when V<sub>c</sub> reaches the threshold voltage (-2.5 V), the depletion layer in the InAIN layer expands to the heterojunction interface, then the 2DEG in the channel depletes and the channel is pinched off. As depicted in Figure 9b, corresponding to magnification of the red circled area shown in Figure 9a, few electrons exist at the InAIN/GaN interface when the device is under off-state. The background carriers in the UID GaN buffer layer forms a leakage channel when the HEMT is at off-state, therefore, it is necessary to introduce acceptor type traps in the forbidden band of the UID GaN buffer layer to capture electrons in the conduction band which can compensate these background electrons [40,41]. Figure 10 obviously exhibits that the background electron concentration in the UID GaN buffer layer decreases as the trap depth increases. The background electron concentrations in the UID GaN buffer layers with trap levels of 0.3, 0.36, 0.42, 0.6, and 0.95 eV are  $1 \times$  $10^{12}$ ,  $1 \times 10^{11}$ ,  $1 \times 10^{10}$ ,  $1 \times 10^{7}$ , and  $1 \times 10^{1}$  cm<sup>-3</sup>, respectively. Based on the analysis mentioned above, the value of  $R_{net}^{SRH}$  increases as the trap level increases. Thus, more electrons are captured to compensate these background electrons as the energy level of trap increases, inducing smaller leakage current.

# Conclusions

In summary, a lattice-matched InAIN/GaN HEMT with appropriate barrier thickness is designed to investigate the effects of trap level in the UID GaN buffer layer on the DC performance of the devices. It is found that different depths of trap level can influence the  $I_{D,max}$  and off-state leakage current of the HEMTs, which is due to that less electrons are captured from the conduction band with shallower trap level. Therefore, more electrons are collected at the InAIN/GaN interface, resulting in deeper potential well in the conduction band.

### Acknowledgments

This work is supported by the National Natural Science Foundation of China (No. 51405198), Natural Science Foundation of Jiangsu Province (No. BK20130159), China Postdoctoral Science Foundation (No. 2016M590406), Six talent peaks project in Jiangsu Province (No. GDZB-138), and Industry-University-Research collaboration project in Jiangsu Province (No. 2018-178).

### References

- 1 Mishra UK, Parikh P, Wu YF (2002) AlGaN/GaN HEMTs-an overview of device operation and applications. Proc IEEE 90: 1022-1031.

- 2 Mishra UK, Shen L, Kazior TE, Wu YF (2008) GaN-Based RF Power Devices and Amplifiers. Proc IEEE 96: 287-305.

- 3 Visalli D, Van Hove M, Derluyn J, Degroote S, Leys M, et al. (2009) AlGaN/GaN/AlGaN double heterostructures on silicon substrates for high breakdown voltage field-effect transistors with low onresistance. J Appl Phys 48: 04C101.

- 4 Kuzuhara M, Tokuda H (2015) Low-loss and high-voltage III-nitride transistors for power switching applications. IEEE Trans Electron Devices 62: 405-413.

- 5 Yang GF, Zhang Q, Wang J, Gao SM, Zhang R, et al. (2015) Analysis of 270/290/330-nm AlGaN-Based Deep Ultraviolet Light-Emitting Diodes with Different Al Content in Quantum Wells and Barriers. IEEE Photonics J 7: 1-7.

- 6 Wu YF, Saxler A, Moore M, Smith RP, Sheppard S, et al. (2004) 30-W/ mm GaN HEMTs by field plate optimization. IEEE Electr Device I 25: 117-119.

- 7 Yao C, Ye X, Sun R, Yang G, Wang J, et al. (2017) High-performance AlGaN-based solar-blind avalanche photodiodes with dual-periodic III–nitride distributed Bragg reflectors. Appl Phys Express 10: 034302.

- 8 Yao C, Ye X, Sun R, Yang G, Wang J, et al. (2017) AlGaN solarblind avalanche photodiodes with AlInN/AlGaN distributed Bragg reflectors. J Appl Phys 123: 439.

- 9 Neuburger M, Zimmermann T, Kohn E, Dadgar A, Schulze F, et al. (2004) Unstrained InAIN/GaN hemt structure. Int J High Speed Electron Syst 14: 785-790.

- 10 Kuzmik J, Kostopoulos A, Konstantinidis G, Carlin JF, Georgakilas A, et al. (2006) InAIN/GaN HEMTs: a first insight into technological optimization. IEEE Trans Electron Devices 53: 422-426.

- 11 Hiroki M, Maeda N, Kobayashi T (2009) Electrical properties and device characteristics of InAIN/AIGaN/AIN/GaN heterostructure field effect transistors. Phys Stat Sol 6: S1056-S1060.

- 12 Kuzmík J (2001) Power electronics on InAlN/(In)GaN: Prospect for a record performance. IEEE Electron Dev Lett 22: 510-512.

- 13 Medjdoub F, Carlin JF, Gaquiere C, Grandjean N, Kohn E (2008) Status of the emerging InAIN/GaN power HEMT technology. Open Electrical & Electronic Engineering Journal 2: 1-7.

- 14 Polyakov AY, Smirnov NB, Shchemerov IV, Yang J, Ren F, et al. (2018) Trapping Phenomena in InAIN/GaN High Electron Mobility Transistors. J Solid State Sci Technol 7: Q1-Q7.

- 15 Kumar S, Remesh N, Dolmanan SB, Tripathy S, Raghavan S, et al. (2017) Interface traps at Al<sub>2</sub>O<sub>3</sub>/InAlN/GaN MOS-HEMT-on-200 mm Si. Solid State Electron 1: 117-122.

- 16 Molnar M, Donoval D, Kuzmik J, Marek J, Chvala A, et al. (2014)

Simulation study of interface traps and bulk traps in n++ GaN/InAlN/ AlN/GaN high electron mobility transistors. Appl Therm Eng. 312: 157-161.

- 17 Auret FD, Goodman SA, Koschnick FK, Spaeth JM, Beaumont B, et al. (1999) Sputter deposition-induced electron traps in epitaxially grown n-GaN. Appl Phys Lett 74: 2173-2175.

- 18 Fang ZQ, Look DC, Visconti P, Wang DF, Lu CZ, et al. (2001) Deep centers in a free-standing GaN layer. Appl Phys Lett 78: 2178-2180.

- 19 Look DC, Fang ZQ (2001) Characterization of near-surface traps in semiconductors: GaN. Appl Phys Lett 79: 84-86.

- 20 Kuzmik J, Carlin JF, Gonschorek M, Kostopoulos A, Konstantinidis G, et al. (2007) Gate-lag and drain-lag effects in (GaN)/InAIN/GaN and InAIN/AIN/GaN HEMTs. Phys Stat Sol 204: 2019-2022.

- 21 Noda N, Tsurumaki R, Horio K (2016) Analysis of lags and current collapse in field-plate AlGaN/GaN HEMTs with deep acceptors in a buffer layer. Phys Status Solidi C 13: 341-344.

- 22 Yan DW, Ren DWJ, Yang GF, Xiao SQ, Gu XF, et al. (2015) Surface Acceptor-Like Trap Model for Gate Leakage Current Degradation in Lattice-Matched InAIN/GaN HEMTs. IEEE Electron Dev Lett 36: 1281-1283.

- 23 Martin-Horcajo S, Wang A, Bosca A, Romero MF, Tadjer MJ, et al. (2015) Trapping phenomena in AlGaN and InAlN barrier HEMTs with different geometries. Semicond Sci Technol 30: 035015.

- 24 Götz W, Johnson NM, Amano H, Akasaki I (1994) Deep level defects in n-type GaN. Appl Phys Lett 65: 463-465.

- 25 Hacke P, Detchprohm T, Hiramatsu K, Sawaki N, Tadatomo K, et al. (1994) Analysis of deep levels in n-type GaN by transient capacitance methods. Appl Phys 76: 304-309.

- 26 Cho HK, Kim KS, Hong CH, Lee HJ (2001) Electron traps and growth rate of buffer layers in unintentionally doped GaN. J Crystal Growth 223: 38-42.

- 27 Polyakov AY, Lee IH (2015) Deep traps in GaN-based structures as affecting the performance of GaN devices. Materials Science and Eng Reports 94: 1-56.

- 28 Hierro A, Kwon D, Ringel SA, Hansen M, Speck JS, et al. (2000) Optically and thermally detected deep levels in n-type Schottky and p+-n GaN diodes. Appl Phys Lett 76: 3064-3066.

- 29 Faramehr S, Kalna K, Igic P (2014) Modeling of 2DEG and 2DHG in i-GaN capped AlGaN/AIN/GaN HEMTs: 29<sup>th</sup> International Conference on Microelectronics, Belgrade.

- 30 Ochiai M, Akita M, Ohno Y, Kishimoto S, Maezawa K, et al. (2003) AlGaN/GaN heterostructure metal-insulator-semiconductor highelectron-mobility transistors with  $Si_3N_4$  gate insulator. Jap j Appl Phys 42: 2278-2280.

- 31 Xue J, Zhang J, Hao Y (2016) Demonstration of InAlN/AlGaN high electron mobility transistors with an enhanced breakdown voltage by pulsed metal organic chemical vapor deposition. Appl Phys Lett 108: 013508.

- 32 Goswami A, Trew RJ, Bilbro GL (2014) Physics of gate leakage current in N-polar InAlN/GaN heterojunction field effect transistors. Appl Phys 116: 164508.

- 33 Morkoç H, Cingolani R, Gil B (1999) Polarization effects in nitride semiconductor device structures and performance of modulation doped field effect transistors. Solid-State Electron 43: 1909-1927.

- 34 Ambacher O, Smart J, Shealy JR, Weimann NG, Chu K, et al. (2000) Two-dimensional electron gases induced by spontaneous and piezoelectric polarization charges in N- and Ga-face AlGaN/GaN heterostructures. J Appl Phys 85: 3222-3233.

- 35 Ambacher O, Majewski J, Miskys C, Link A, Hermann M, et al. (2002) Pyroelectric properties of Al (In) GaN/GaN hetero-and quantum well structures. J Phys Condens Matter 14: 3399-3434.

- 36 Silvaco Int (2016) Atlas user's manual device simulation software. Santa Clara. Available from: https://www.silvaco.com

- 37 Hall RN (1952) Electron-hole recombination in germanium. Phys Rev 87: 387.

- 38 Shockley W, Read Jr WT (1952) Statistics of the recombination's of holes and electrons. Phys Rev 87: 835-842.

- 39 Pelá RR, Caetano C, Marques M, Ferreira LG, Furthmüller J, et al. (2011) Accurate band gaps of AlGaN, InGaN, and AlInN alloys calculations based on LDA-1/2 approach. Appl Phys Lett 98: 151907.

- 40 Gong JM, Wang Q, Yan JD, Liu FQ, Feng C, et al. (2016) Comparison of GaN/AlGaN/AlN/GaN HEMTs grown on sapphire with Fe-Modulation-Doped and unintentionally doped GaN Buffer: Material growth and device fabrication Chin. Phys Lett 33: 99-103.

- 41 Desmaris V, Rudzinski M, Rorsman N, Hageman PR, Larsen PK, et al. (2006) Comparison of the DC and microwave performance of AlGaN/GaN HEMTs grown on SiC by MOCVD with Fe-doped or unintentionally doped GaN buffer layers. IEEE Trans Electron Devices 53: 2413-2417.